# TARJETA DE DESARROLLO DE SISTEMAS CON TECNOLOGÍA FPGA.

#### **Características Técnicas:**

- FPGA de Xilinx XC2S400E

- ISP PROM XC18V04

- Memoria RAM estática: 2Mbytes

- Memoria FLASH: 4 Mbytes

- Temperatura de almacenamiento: entre −20°C y 80°C.

- Temperatura de funcionamiento: entre 0°C y 60°C.

- Tamaño del módulo: 64x99mm

- Interface RS232

- Alimentación: 5V

- Consumo: 1200 mA

- Conector de expansión de 150 pines

- Conector JTAG

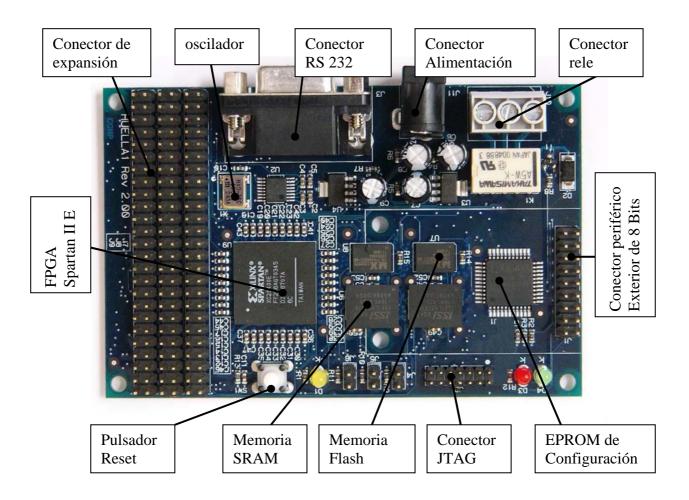

La tarjeta de desarrollo **HUELLA 1** de **Van Microsistemas, SL** es una completa solución para la realización de diseños y aplicaciones, basada en tecnología FPGA y utiliza una Spartan-2E de Xilinx.

El kit consta de una tarjeta, un alimentador de 5V, manual de referencia y un disco con un ejemplo de configuración con un sistema que utiliza un Microblaze con memoria externa SRAM y FLASH, un puerto serie y GPIO.

La tarjeta utiliza un chip de 400.000 puertas Xilinx Spartan2E (XC2S400E-FT256) con una matriz de 256 pines tipo FPGA (fine-pitch ball grid arrays).

Incluye memoria EPROM de configuración de la FPGA, 2 Mbytes de memoria RAM estática (SRAM), 4 Mbytes de memoria FLASH, un puerto serie, conector JTAG y conector de expansión de 150 pines.

La alta densidad de puertos, el gran número de pines entrada/ salida (IOs) así como la memoria externa SRAM y FLASH, permiten al usuario, realizar la implementación de un diseño de bajo coste, en un tiempo record para obtener un producto final. La figura 1 muestra la tarjeta de desarrollo y sus características:

### **FPGA-Spartan 2E**

La tarjeta de desarrollo utiliza el dispositivo FPGA Spartan 2E XC2S400E-FT256. La familia Spartan 2E de 1,8V, da al usuario un gran rendimiento y abundantes recursos lógicos. Internamente contiene 400.000 puertas, 10.800 celdas lógicas, 2.400 CLBs, 153.000 bits de memoria distribuida y 160 Kbits de bloques de RAM.

La familia Spartan 2E es una alternativa avanzada para los programadores de ASICs. FPGA acorta el tiempo de desarrollo de un proyecto y permite la actualización del hardware sin necesidad de reemplazar componentes, cosa imposible en ASICs.

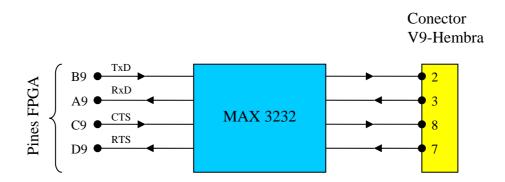

#### **Puerto RS232**

La tarjeta contiene un puerto serie RS232 que se maneja directamente desde la FPGA. Un driver MAX3232 cambia de nivel las señales necesarias para una comunicación serie, TXD, RXD, RTS y CTS.

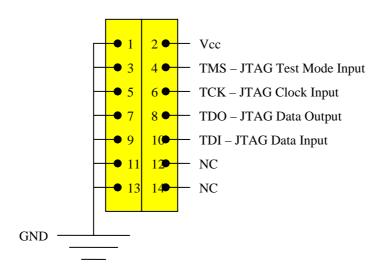

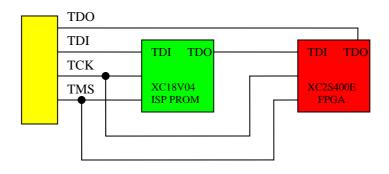

## **Puerto JTAG**

La tarjeta contiene un puerto JTAG que puede ser usado para enviar la configuración de la FPGA directamente desde un PC, ó grabar la configuración de la FPGA en la ISP PROM (XC18V04) para que esta se cargue en la FPGA en el momento de dar alimentación al sistema.

## **Conector JTAG**

# **Cadena JTAG**

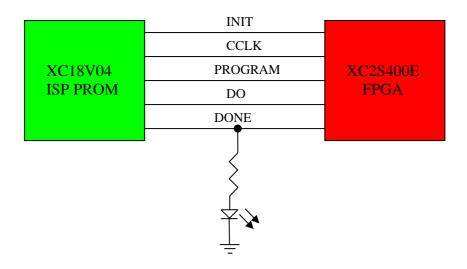

# Conexión ISP PROM-FPGA

# Reguladores de voltaje

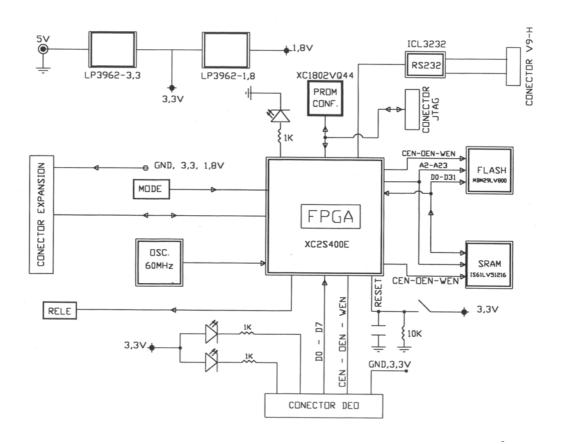

La tarjeta contiene 2 reguladores de voltaje, uno de 3'3V (LP3965-3'3) Para alimentación de los dispositivos externos de la FPGA y puertos de entrada/ salida (VCCO) y otro de 1'8V (LP3965-1'8) para alimentación interna de la FPGA (VCCINT).

Spartan 2E. Modos de configuración

| <u>Modo</u>    | PC pull-up | J4(M0) | J5(M1) | J6(M2) |

|----------------|------------|--------|--------|--------|

| Master serial  | NO         | ON     | ON     | ON     |

| Master serial  | SI         | ON     | ON     | OFF    |

| Slave serial   | NO         | OFF    | OFF    | OFF    |

| Slave serial   | SI         | OFF    | OFF    | ON     |

| Slave parallel | NO         | ON     | OFF    | OFF    |

| Slave parallel | SI         | ON     | OFF    | ON     |

| JTAG           | NO         | OFF    | ON     | OFF    |

| JTAG           | SI         | OFF    | ON     | ON     |

Pines libres de la FPGA que pueden ser usados desde el conector de expansión, para dispositivos externos a la tarjeta. Los marcados I/O son pines de propósito general, CLK entrada de reloj o pines de propósito general.

| 1  | D1  | I/O |     | 3,3 | 2  | 1  | L3  | I/O |     | 3,3 | 2  | 1  | G13 | I/O |     | 3,3 | 2  |

|----|-----|-----|-----|-----|----|----|-----|-----|-----|-----|----|----|-----|-----|-----|-----|----|

| 3  | D3  | I/O | C2  | I/O | 4  | 3  | C1  | I/O | D2  | I/O | 4  | 3  | E14 | I/O | D15 | I/O | 4  |

| 5  | E4  | I/O | E2  | I/O | 6  | 5  | E1  | I/O | F4  | I/O | 6  | 5  | D14 | I/O | B8  | CLK | 6  |

| 7  | F1  | I/O | F5  | I/O | 8  | 7  | G5  | I/O | G3  | I/O | 8  | 7  | A12 | I/O | D12 | I/O | 8  |

| 9  | G1  | I/O | H4  | I/O | 10 | 9  | НЗ  | I/O | H2  | I/O | 10 | 9  | A11 | I/O | E10 | I/O | 10 |

| 11 | J2  | I/O | J3  | I/O | 12 | 11 | J1  | I/O | K1  | I/O | 12 | 11 | C15 | I/O | A14 | I/O | 12 |

| 13 | L1  | I/O | L2  | I/O | 14 | 13 | K4  | I/O | K5  | I/O | 14 | 13 | A7  | I/O | E7  | I/O | 14 |

| 15 | M1  | I/O | N1  | I/O | 16 | 15 | L4  | I/O | L5  | I/O | 16 | 15 | E6  | I/O | D5  | I/O | 16 |

| 17 | N2  | I/O | N3  | I/O | 18 | 17 | P1  | I/O | P2  | I/O | 18 | 17 | P4  | D0  | R4  | D1  | 18 |

| 19 | T13 | I/O | N11 | I/O | 20 | 19 | M11 | I/O | P12 | I/O | 20 | 19 | Т3  | D2  | T4  | D3  | 20 |

| 21 | P13 | I/O | T14 | I/O | 22 | 21 | R14 | I/O | H14 | I/O | 22 | 21 | N5  | D4  | P5  | D5  | 22 |

| 23 | F16 | I/O | H13 | I/O | 24 | 23 | G14 | I/O | F15 | I/O | 24 | 23 | R5  | D6  | T5  | D7  | 24 |

| 25 | F14 | I/O | E15 | I/O | 26 | 25 | D16 | I/O | F13 | I/O | 26 | 25 | N6  | D8  | P6  | D9  | 26 |

| 27 | C16 | I/O | G12 | I/O | 28 | 27 | F12 | I/O | E13 | I/O | 28 | 27 | R6  | D10 | T6  | D11 | 28 |

| 29 | A13 | I/O | B13 | I/O | 30 | 29 | C12 | I/O | B12 | I/O | 30 | 29 | M6  | D12 | N7  | D13 | 30 |

| 31 | E11 | I/O | D11 | I/O | 32 | 31 | C11 | I/O | B11 | I/O | 32 | 31 | P7  | D14 | R7  | D15 | 32 |

| 33 | D10 | I/O | C10 | I/O | 34 | 33 | B10 | I/O | A10 | I/O | 34 | 33 | T7  | D16 | M7  | D17 | 34 |

| 35 | T9  | CLK | Т8  | CLK | 36 | 35 | A8  | I/O | D8  | I/O | 36 | 35 | N8  | D18 | P8  | D19 | 36 |

| 37 | D7  | I/O | A5  | I/O | 38 | 37 | B5  | I/O | D6  | I/O | 38 | 37 | R8  | D20 | P9  | D21 | 38 |

| 39 | C5  | I/O | E3  | I/O | 40 | 39 | M2  | I/O | M3  | I/O | 40 | 39 | N9  | D22 | T10 | D23 | 40 |

| 41 | F3  | I/O | F2  | I/O | 42 | 41 | M4  | I/O | R9  | I/O | 42 | 41 | R10 | D24 | P10 | D25 | 42 |

| 43 | G4  | I/O | G2  | I/O | 44 | 43 | T12 | I/O | N12 | I/O | 44 | 43 | R11 | D26 | T11 | D27 | 44 |

| 45 | H1  | I/O | J4  | I/O | 46 | 45 | R13 | I/O | H15 | I/O | 46 | 45 | N10 | D28 | M10 | D29 | 46 |

| 47 | K2  | I/O | К3  | I/O | 48 | 47 | G15 | I/O | E16 | I/O | 48 | 47 | P11 | D30 | R12 | D31 | 48 |

| 49 | Gnd |     | gnd |     | 50 | 49 | gnd |     | gnd |     | 50 | 49 | gnd |     | gnd |     | 50 |

|    |     |     |     |     | -  |    |     | ·   |     | ·   | -  |    |     |     |     |     | _  |

El software y cables necesarios para desarrollar con la Spartan 2E de Xilinx es el siguiente:

- **ISE**

- **EDK**

- **MODELSIM**

- PARALLEL CABLE IV

- Opcionalmente CHIPSCOPE PRO ANALIZER

Estos pueden adquirirse en SILICA, una compañía de Avnet representante de Xilinx en España. (Sergio Ocaña 00 34 913727146)